最近拿到了基于ZYNQ 7020器件的PYNQ开发板,便有了这篇体验文章。本文首先进行常规的开箱和初见印象描述;随后尝试解释了ZYNQ这一硬件的特色;最后以目标检测为例,体验了PYNQ的开发流程。

Table of Contents

之前接近半年的时间都在使用ZYNQ这款器件,并用ZYNQ这款器件完成我的毕业设计。

有幸的是,Xilinx家的官方开发板,从zc706,到zcu102、zcu106,我都有实际地使用过。

实事求是地讲,作为一个软件开发者,ZYNQ这种ARM+FPGA的架构,在我这里的开发思路更像是个大个儿树莓派+FPGA协处理器。由于涉及到了FPGA硬件,若要发挥出其最大的优势,开发思路并不是码完代码直接跑这样单纯。关于这点在下文中将尝试对ZYNQ进行解释,ZYNQ是个比较有趣的硬件平台。

本文首先进行常规的开箱和初见印象描述,随后尝试解释了ZYNQ这一硬件的特色。最后以目标检测为例,体验了PYNQ的开发流程。

1 开箱与初见

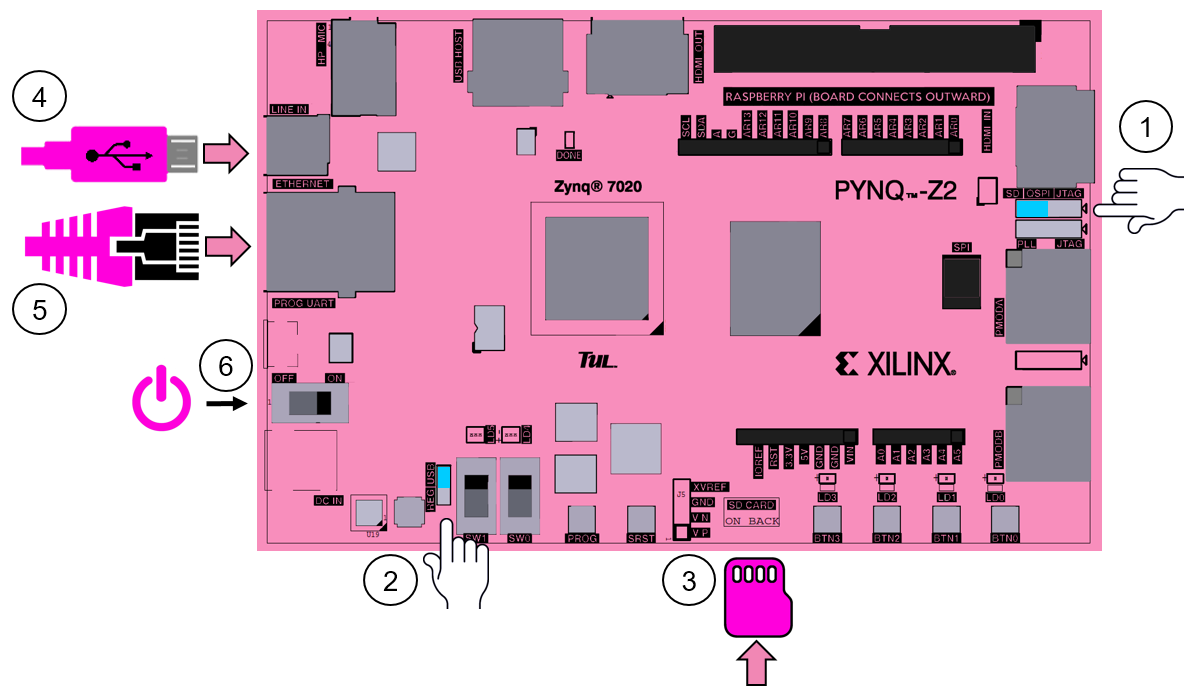

我拿到的是PYNQ Z2版本,是由Tul出品的。在国内依元素大学计划拿到,开发板套装1350元。包装比较简洁,附带电源适配器网线亚克力壳等等。

板子正面比较简洁。整体色调为粉色。第一眼可以看到有数个PMOD接口、Raspberry Pi兼容接口、Arduino 拓展板接口。核心器件 ZYNQ7020已经被散热片覆盖。

在官方推崇的主流开发流程中,只需网线和供电,配合jupyter即可完成大部分开发操作。

因此大部分情况下,它通过Ethernet接入你的PC或者局域网后,只需安静地躺在桌子旁边。必要时可连接USB URAT进行debug。

PYNQ Z2的简要规格如下,我关心的一些参数加粗了:

| ZYNQ XC7Z020-1CLG400C • 650MHz dual-core Cortex-A9 processor • DDR3 memory controller with 8 DMA channels and 4 High Performance AXI3 Slave ports • High-bandwidth peripheral controllers: 1G Ethernet, USB 2.0, SDIO • Low-bandwidth peripheral controller: SPI, UART, CAN, I2C • Programmable from JTAG, Quad-SPI flash, and MicroSD card • Programmable logic equivalent to Artix-7 FPGA • 13,300 logic slices, each with four 6-input LUTs and 8 flip-flops • 630 KB of fast block RAM • 4 clock management tiles, each with a phase locked loop (PLL) and mixed-mode clock manager (MMCM) • 220 DSP slices • On-chip analog-to-digital converter (XADC) Memory • 512MB DDR3 with 16-bit bus @ 1050Mbps • 16MB Quad-SPI Flash with factory programmed 48-bit globally unique EUI-48/64™ compatible identifier • MicroSD slot Power • Powered from USB or 7V-15V external power source |

USB and Ethernet • Gigabit Ethernet PHY • Micro USB-JTAG Programming circuitry • Micro USB-UART bridge • USB 2.0 OTG PHY (supports host only) Audio and Video • HDMI sink port (input) • HDMI source port (output) • I2S interface with 24bit DAC with 3.5mm TRRS jack • Line-in with 3.5mm jack Switches, Push-buttons and LEDs • 4 push-buttons • 2 slide switches • 4 LEDs • 2 RGB LEDs Expansion Connectors • Two standard Pmod ports • 16 Total FPGA I/O (8 shared pins with Raspberry Pi connector) • Arduino Shield connector • 24 Total FPGA I/O • 6 Single-ended 0-3.3V Analog inputs to XADC • Raspberry Pi connector • 28 Total FPGA I/O (8 shared pins with Pmod A port) |

2 ZYNQ与PYNQ

2.1 ZYNQ片上系统

ZYNQ是Xilinx出品的片上系统(SoC,System On Chip)。SoC指单个硅芯片可以来实现整个系统的功能,往往该系统可能需要多个不同的芯片。在消费电子中,你可能比较熟悉高通的手机处理器骁龙系列,没错,骁龙就是典型的SoC,它在一片SoC上集成了移动宽带解调与多媒体、3D图形、GPS等功能。SoC意味着是解决方案,往往有着更好的数据传输、更低功耗和更小的空间占用。

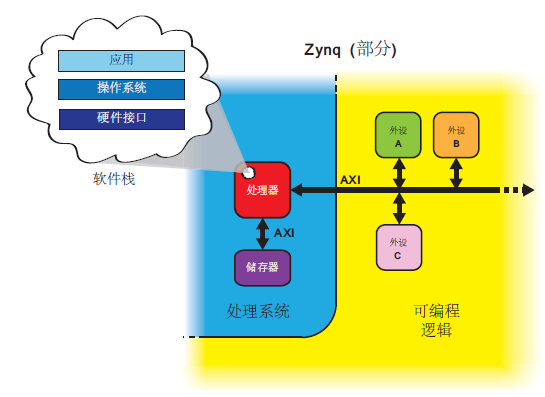

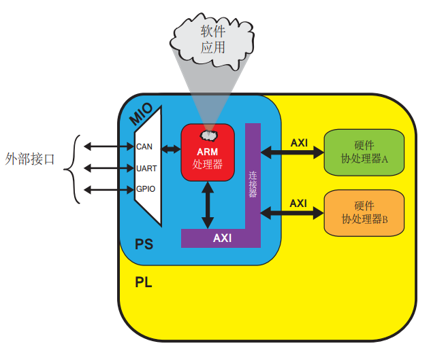

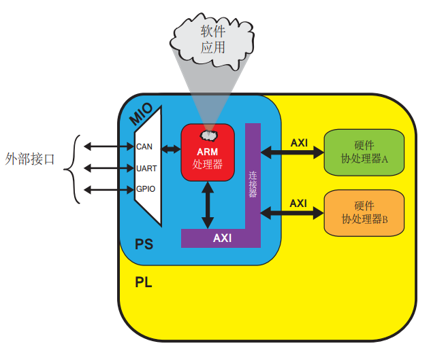

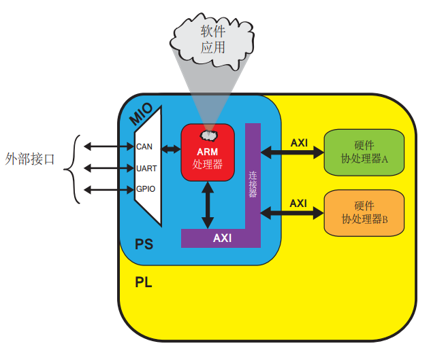

我们今天的主角ZYNQ的架构图如下。在这一片SoC中,将处理系统Process System和可编程逻辑Programmable System集合起来,其间使用片内AXI总线连接。

图: Zynq架构简化模型[Zynq Book - http://www.zynqbook.com/]

2.1.1 处理系统Process System

处理系统为上述蓝色部分,简称PS端。在一片典型的Zynq 7000系列SoC上,可以是:

- 双核ARM Cortex-A9处理器

看到这里熟悉ARM的同学会明白,如果单看PS端,它就是一片基于ARM的处理器,可以用来支撑部分硬件接口、操作系统、应用层程序。

事实上,把它当普通的ARM来进行软件开发没有任何不妥。

2.1.2 可编程逻辑Programmable System

黄色部分为可编程逻辑,简称PL端。在一片典型的Zynq 7000系列SoC上,可以是:

- Artix-7 FPGA

FPGA的全称是Field-Programmable Gate Array,现场可编程门阵列。简单理解,它就是一块可以硬件地编程的胶水硬件,由无数个可编程逻辑门组成。我们可以在上“定制”出我们自己想要的专属硬件。

2.1.3 协同工作

PL 和PS 之间的链接采用了片内AXI总线连接,速度比较理想。

上面已经介绍了PS端和PL端。

软件(PS端)擅长完成一般性的顺序执行任务,如OS、Application和GUI。

硬件(PL端)市场进行数据流计算的任务,尤其是具有并行限制的软件算法。

PL 部分用来实现高速逻辑、算术和数据流子系统是很理想的,而PS支持软件程序和/或操作系统,这就意味着任何被设计的系统的整个功能可以恰当地在硬件和软件之间做出划分。

系统架构的设计通常是自上而下的方法。 那就是先确定顶层的接口和参数,确定底层的子系统或功能。 根据需要将设计适当地分为硬件和软件,并在系统定义中定义必要的通信。

因此,ZYNQ的方法论可以归结如下:

- 一般逻辑算法在ARM端运行

- 大量计算卸载到FPGA端运行

- ARM+FPGA高速互联、协同运行

2.1.4 优势和劣势

优势很明显,如此结合的SoC在某些场景,尤其是需要将系统的整个功能可以恰当地在硬件和软件之间做出划分,结合ARM+FPGA优势的场景,ZYNQ会获得天生的集成度。

然而我不是来做广告的。我必须指出它的劣势:

价格

可以尝试在贸泽电子搜索对比器件价格。ZYNQ的价格绝对说不上低,在量产的情形下,几分几毛钱都值得细究。至于是否上一片ZYNQ,用ARM+FPGA的优势,还是上一篇高性能的其他处理器尝试解决问题,就值得思考了。

开发难度

FPGA对于软件工程师绝对不算友好。可能Xilinx也在考虑这方面,尤其近年来推出了一些结合PS和PL端的开发工具SDSoC,和一些软件栈,来吸引软件工程师,尤其是近年来大火的机器学习、边缘计算应用。但一点点细抠PL端的硬件设计,哪有我用Python在应用层上码代码,立即运行&所见即所得来的开心呢?性能不够我就上志强、堆GPU嘛,反正OpenCV、Caffe等等都自带CUDA驱动。

上升一下,去大学随便看一看,CS的毕业生的毕设有多少人做软件应用?又有几个人做硬件设计?人生苦短。

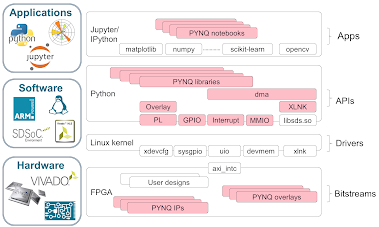

2.2 PYNQ

PYNQ是Xilinx公司的开源项目,只在使用Python语言和库,让开发者可以更方便的基于ZYNQ创建高性能嵌入式系统,更方便的使用PS-PL结合。

- 并行硬件执行

- 高帧率视频处理

- 硬件加速算法

- 实时信号处理

- 高带宽IO

- 低延迟控制

PYNQ试图将设计流程变得更加友好,面向系统架构师和软件开发工程师。

- 希望利用Zynq和可编程硬件功能而无需使用ASIC式设计工具来设计硬件的软件开发人员。

- 系统架构师需要一个简单的软件界面和框架来快速进行原型设计和Zynq设计的开发。

- 希望他们的设计被最广泛的受众使用的硬件设计师。

PYNQ使用Jupyter Notebook,直接使用基于浏览器对硬件进行交互。

项目官网和文档见 http://www.pynq.io/

个人理解,PYNQ更像是一个创客的玩具。它试图将设计流程变得更加友好,Python也迎合了很多软件开发者的口味。为了更加友好地使用PL端,PYNQ提供了overlay。

Overlay是PYNQ的一个重要概念。官方的描述值得寻味:

PYNQ提供了一个Python接口,允许通过PS中运行的Python控制PL中的Overlay。FPGA设计是一项需要硬件工程知识和专业知识的专业任务。PYNQ的Overlay层由硬件设计人员创建,并包含在此PYNQ Python API中。然后,软件开发人员可以使用Python接口来编程和控制专用硬件Overlay,而无需自己设计。

这类似于由专家开发人员创建的软件库,然后由在应用程序级别工作的许多其他软件开发人员使用。

说的确实有道理,难道我们在写应用层程序时候,不也是用一些常用的轮子软件库吗?

如果你看了上面的话感到一头雾水,可以结合上图理解:

作为一篇开箱文,关于Overlay的自定义不在本文中阐述。但是关于Overlay的使用,将在下章涉及。

3 开发流程 - 以目标检测应用为例

说了这么多,我们马上来进入PYNQ的应用层开发吧!

本章首先介绍了PYNQ板卡的准备,然后简单介绍了Tiny YOLO目标检测算法的原理,最后记录了实验结果。

3.1 Get Started

首先我们熟悉一下PYNQ的开发流程。

图:PYNQ上手流程[https://pynq.readthedocs.io/en/latest/getting_started.html]

和任何一块开发板上手一样,根据官方引导,首先设置好板上跳帽,烧写好TF卡镜像,开机。

PYNQ推荐将它接入到你的局域网中,或者用以太网连接PC。在官方推崇的主流开发流程中,只需网线和供电,配合jupyter即可完成大部分开发操作。

接入局域网后,由于PYNQ默认的hostname为“PYNQ”,因此,你可以在浏览器中直接输入 http://PYNQ 进入Jupyter notebook。

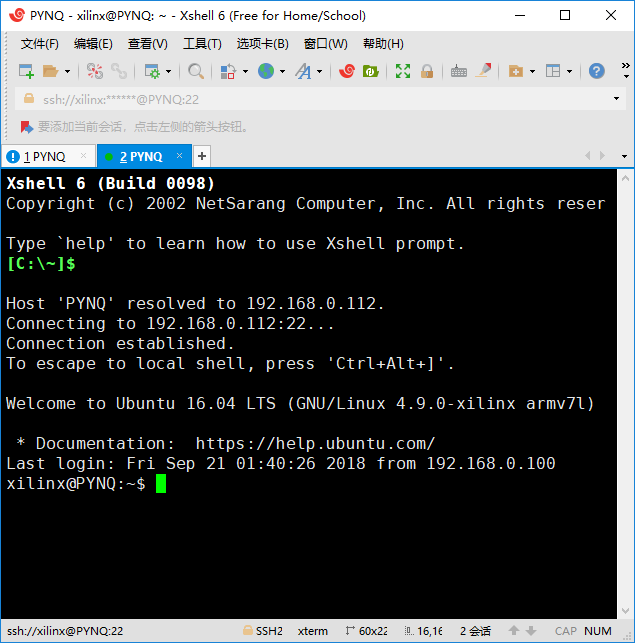

在Jupyter notebook中即可完成大部分Python程序的编写任务,能够获得输入和输出。同时Jupyter notebook也提供了终端模拟器,可以直接从浏览器管理开发板上的Linux。

当然,我已经习惯了用终端来管理我的Linux主机。因此我使用Jupyter notebook + Xshell作为我自己的开发环境。

如果你熟悉Linux,应该已经理解,其将之前较为复杂的ZYNQ开发流程变成了简单易懂的板上Python开发方式。在原本嵌入式Linux的基础上提供了Jupyter notebook,更为方便。

顺带一提,官方的镜像基于Ubuntu 16.04 LTS,架构为armv7l。

当然,我更加习惯使用UART串口直接进行板上开发……一下接触了方便的东西反而不适应了……

OK,在PYNQ编写Python程序已经如此简洁,参考:https://pynq.readthedocs.io 查看Python环境、库的信息、overlay的用法等等。

3.2 Tiny YOLO目标检测算法

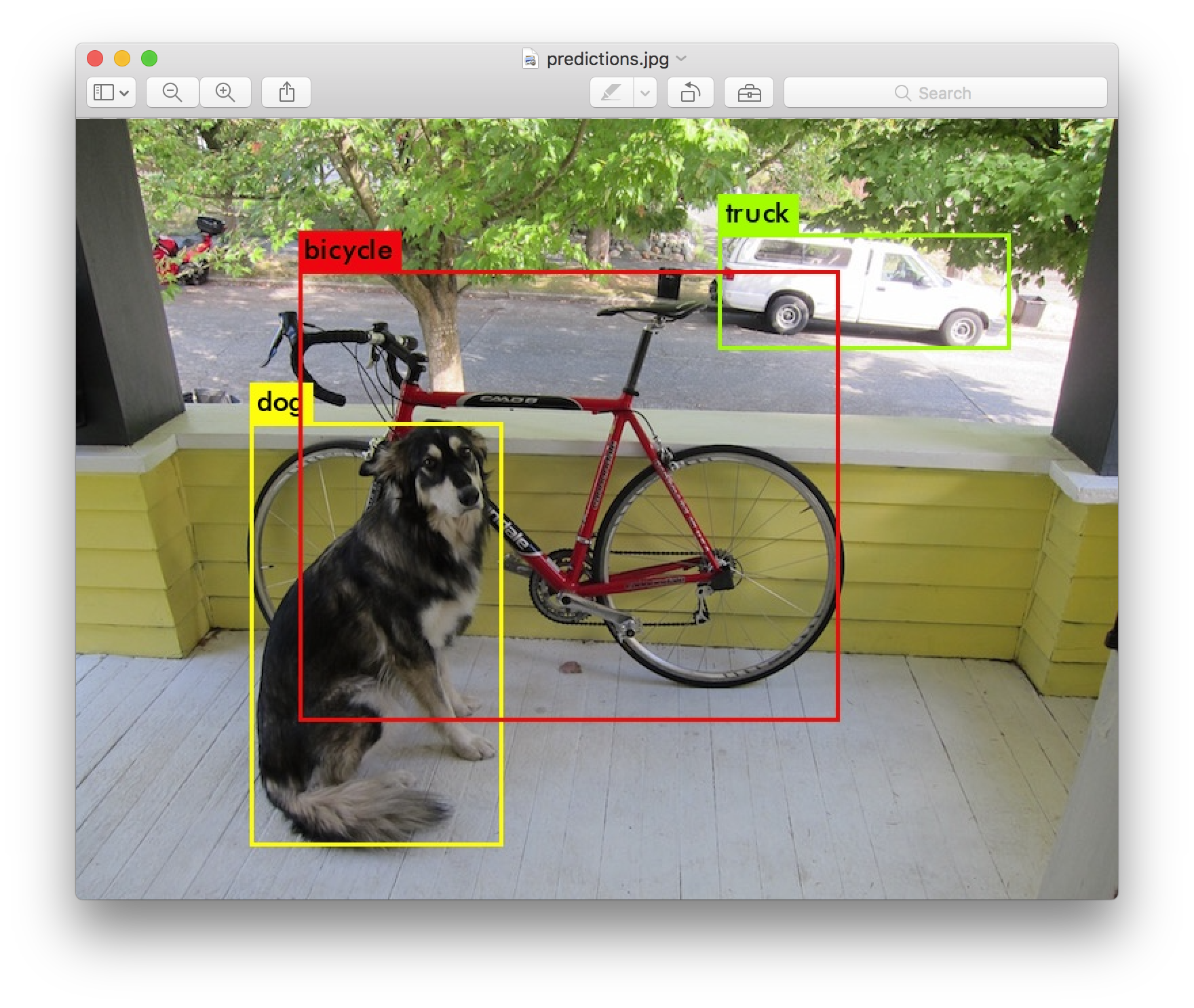

YOLO是一个神一样的目标检测算法。目标检测,简单来说,输入是一幅图像,输出是检测出目标的类型和图像中的位置。

图:YOLO v3输出示例[https://pjreddie.com/darknet/yolo/]

作者项目地址为

https://pjreddie.com/darknet/yolo/

YOLO在工业界也是非常受欢迎的目标检测算法,它精度和速度都很不错,大牛作者也很可爱,感兴趣的同学可以检索下,或者看下近年来目标检测的综述。

3.3 QNN-MO-PYNQ 官方机器学习库

这次我们使用的项目为Xilinx官方的为PYNQ设计的机器学习示例:

https://github.com/Xilinx/QNN-MO-PYNQ

项目中使用的是修改后的Tiny YOLO模型,叫做Tinier-YOLO。在VOC数据集上训练,使用了1bit的权重层和3bit的激活层。

模型如下[https://github.com/Xilinx/QNN-MO-PYNQ]:

3.3.1 安装

首先pip安装:

# (on PYNQ v2.1) sudo pip3.6 install git+https://github.com/Xilinx/QNN-MO-PYNQ.git

如果报错SSL证书问题,检查你PYNQ板上的时间!如果时间早于目前时间,可能造成SSL整数不生效导致Https拉取失败。

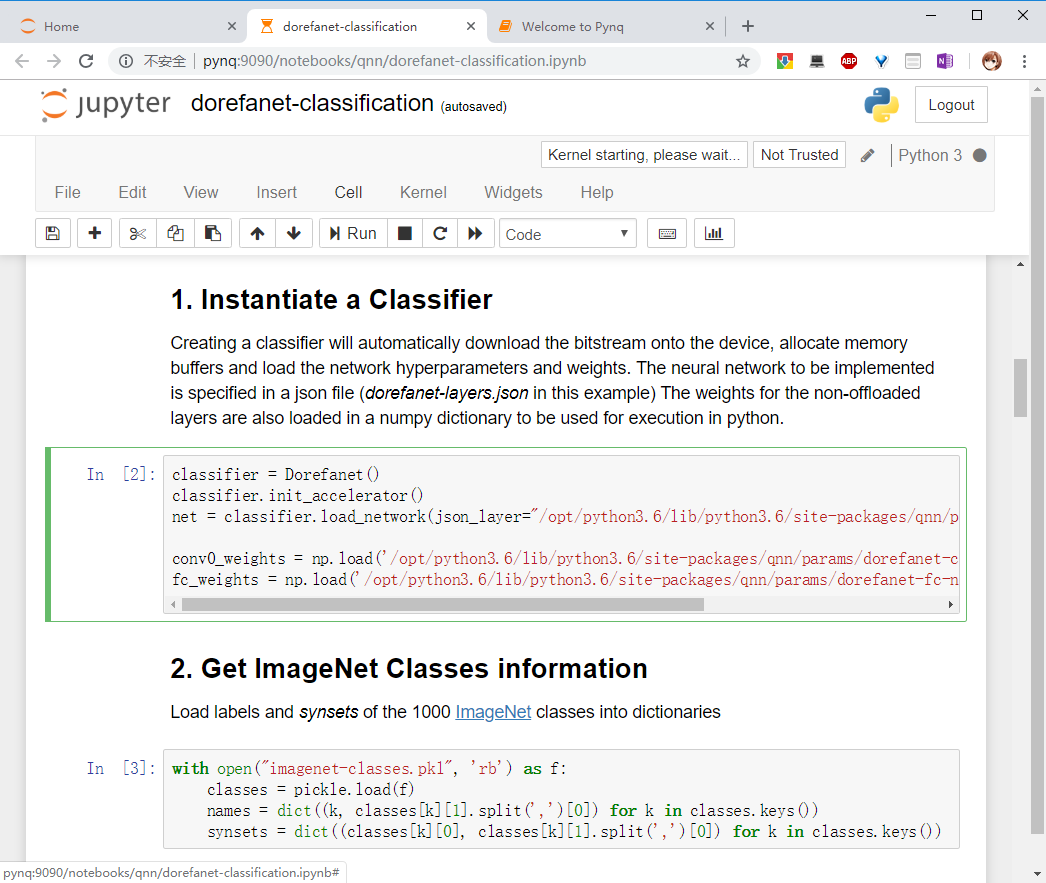

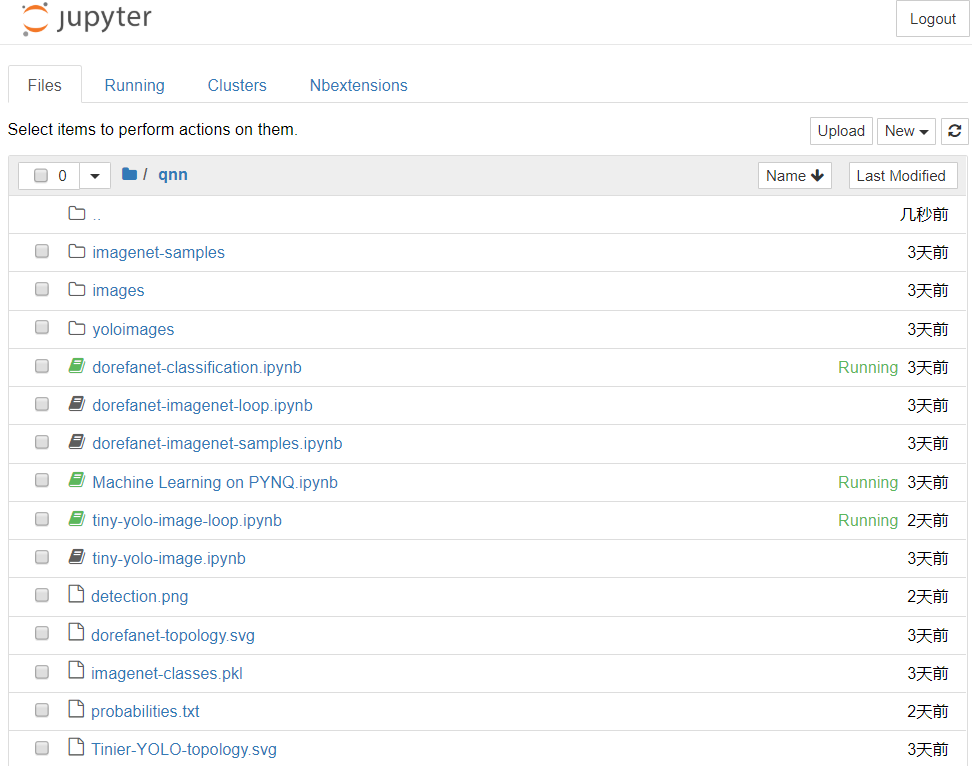

安装完成后,我们可以看到在jupyter中出现了我们刚才安装的库用例。

3.3.2 初始化

打开tiny-yolo-image-loop.ipynb即可运行我们的Tiny YOLO。但是我们也看下其中的逻辑:

import sys

import os, platform

import json

import numpy as np

import cv2

import ctypes

from matplotlib import pyplot as plt

from PIL import Image

from datetime import datetime

from qnn import TinierYolo

from qnn import utils

sys.path.append("/opt/darknet/python/")

from darknet import *

%matplotlib inline

import IPython

首先导入必要的库。我们在pip安装的时候,安装了qnn库和yolo算法的Darknet库。

classifier = TinierYolo()

classifier.init_accelerator()

net = classifier.load_network(json_layer="/opt/python3.6/lib/python3.6/site-packages/qnn/params/tinier-yolo-layers.json")

conv0_weights = np.load('/opt/python3.6/lib/python3.6/site-packages/qnn/params/tinier-yolo-conv0-W.npy', encoding="latin1")

conv0_weights_correct = np.transpose(conv0_weights, axes=(3, 2, 1, 0))

conv8_weights = np.load('/opt/python3.6/lib/python3.6/site-packages/qnn/params/tinier-yolo-conv8-W.npy', encoding="latin1")

conv8_weights_correct = np.transpose(conv8_weights, axes=(3, 2, 1, 0))

conv0_bias = np.load('/opt/python3.6/lib/python3.6/site-packages/qnn/params/tinier-yolo-conv0-bias.npy', encoding="latin1")

conv0_bias_broadcast = np.broadcast_to(conv0_bias[:,np.newaxis], (net['conv1']['input'][0],net['conv1']['input'][1]*net['conv1']['input'][1]))

conv8_bias = np.load('/opt/python3.6/lib/python3.6/site-packages/qnn/params/tinier-yolo-conv8-bias.npy', encoding="latin1")

conv8_bias_broadcast = np.broadcast_to(conv8_bias[:,np.newaxis], (125,13*13))

file_name_cfg = c_char_p("/opt/python3.6/lib/python3.6/site-packages/qnn/params/tinier-yolo-bwn-3bit-relu-nomaxpool.cfg".encode())

net_darknet = lib.parse_network_cfg(file_name_cfg)

然后创建分类器,初始化我们的加速器。

如果你熟悉Darknet框架,一定很眼熟其中的配置文件形式和权重形式。

在这个过程中,我们的加速器Overlay被示例化进我们的FPGA中,成为了我们的硬件协加速器!该加速器已经由库设计好。当然,在以后的进阶开发中,我们可以创建自己的协加速器。

具体的Overlay比特流如下(bitstream,可以理解成描述FPGA加速器的文件)。

3.3.3 软硬协同前向推理

out_dim = net['conv7']['output'][1]

out_ch = net['conv7']['output'][0]

img_folder = './yoloimages/'

file_name_out = c_char_p("/home/xilinx/jupyter_notebooks/qnn/detection".encode())

file_name_probs = c_char_p("/home/xilinx/jupyter_notebooks/qnn/probabilities.txt".encode())

file_names_voc = c_char_p("/opt/darknet/data/voc.names".encode())

tresh = c_float(0.3)

tresh_hier = c_float(0.5)

darknet_path = c_char_p("/opt/darknet/".encode())

conv_output = classifier.get_accel_buffer(out_ch, out_dim)

while(1):

for image_name in os.listdir(img_folder):

img_file = os.path.join(img_folder, image_name)

file_name = c_char_p(img_file.encode())

img = load_image(file_name,0,0)

img_letterbox = letterbox_image(img,416,416)

img_copy = np.copy(np.ctypeslib.as_array(img_letterbox.data, (3,416,416)))

img_copy = np.swapaxes(img_copy, 0,2)

free_image(img)

free_image(img_letterbox)

#First convolution layer in sw

if len(img_copy.shape)<4:

img_copy = img_copy[np.newaxis, :, :, :]

conv0_ouput = utils.conv_layer(img_copy,conv0_weights_correct,b=conv0_bias_broadcast,stride=2,padding=1)

conv0_output_quant = conv0_ouput.clip(0.0,4.0)

conv0_output_quant = utils.quantize(conv0_output_quant/4,3)

#Offload to hardware

conv_input = classifier.prepare_buffer(conv0_output_quant*7);

classifier.inference(conv_input, conv_output)

conv7_out = classifier.postprocess_buffer(conv_output)

#Last convolution layer in sw

conv7_out = conv7_out.reshape(out_dim,out_dim,out_ch)

conv7_out = np.swapaxes(conv7_out, 0, 1) # exp 1

if len(conv7_out.shape)<4:

conv7_out = conv7_out[np.newaxis, :, :, :]

conv8_output = utils.conv_layer(conv7_out,conv8_weights_correct,b=conv8_bias_broadcast,stride=1)

conv8_out = conv8_output.ctypes.data_as(ctypes.POINTER(ctypes.c_float))

#Draw detection boxes

lib.forward_region_layer_pointer_nolayer(net_darknet,conv8_out)

lib.draw_detection_python(net_darknet, file_name, tresh, tresh_hier,file_names_voc, darknet_path, file_name_out, file_name_probs);

#Display result

IPython.display.clear_output(1)

file_content = open(file_name_probs.value,"r").read().splitlines()

detections = []

for line in file_content[0:]:

name, probability = line.split(": ")

detections.append((probability, name))

for det in sorted(detections, key=lambda tup: tup[0], reverse=True):

print("class: {}\tprobability: {}".format(det[1], det[0]))

res = Image.open(file_name_out.value.decode() + ".png")

display(res)

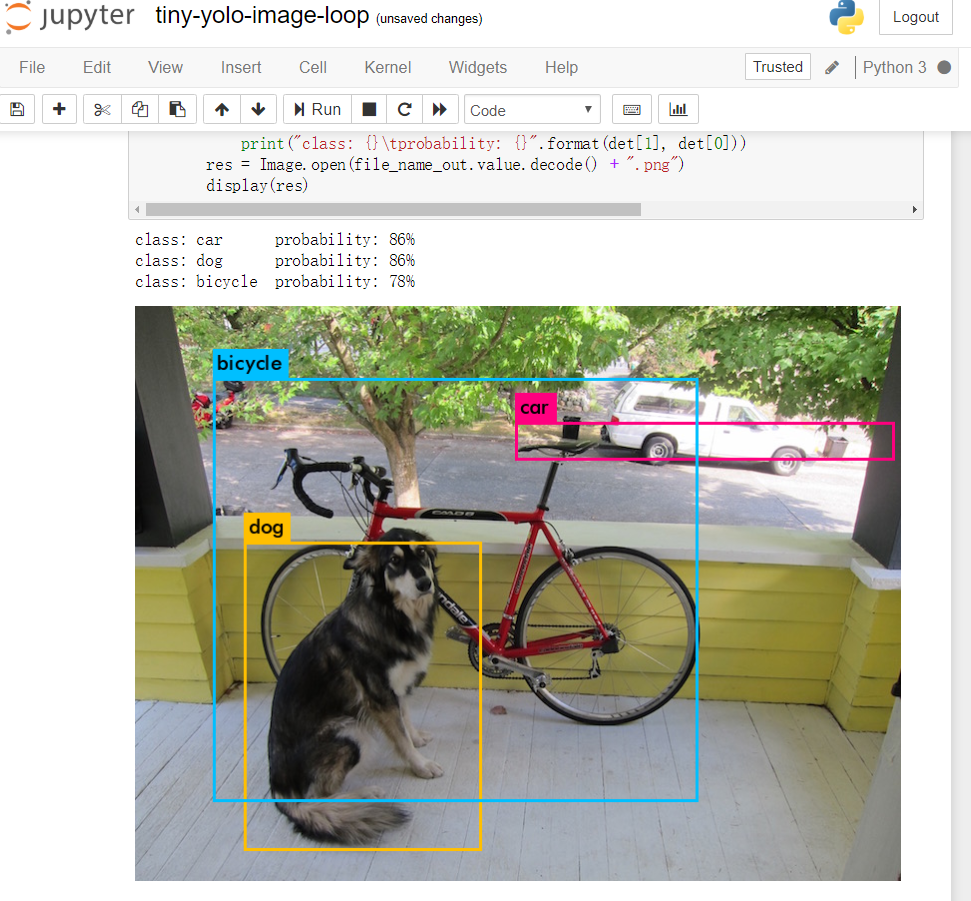

随后是大循环,不断地载入图片,前向推理。最终输出结果。

还记得我们刚才画的模型图吗?YOLO的特点是这样,在一端将图像的像素信息输入,经过前向推理计算,就可以得到检测结果。

在前向推理的过程中,卷积层计算占用了绝大部分时间,因此我们要使用硬件加速的overlay加速我们计算密集的部分。

值得注意的是,在本DEMO中,第一层和最后一层是用CPU软件算的,其余层使用了FPGA硬件协加速器。

3.3.4 重置退出

安全退出的方法。

classifier.deinit_accelerator() from pynq import Xlnk xlnk = Xlnk(); xlnk.xlnk_reset()

3.4 结果

jupyter输出如下:

jupyter确实方便,能将结果直接输出出来方便调试。

输出精度大致可以接受,毕竟是Tiny YOLO的简化版。

输出速度,大概是3秒/1帧。注意,不是1秒3帧,是3秒1帧。

考虑到ZYNQ7020不到5w的功耗,和嵌入式ARM的计算能力,这个成绩符合我的预料。根据我之前Darknet框架的实验,Tiny YOLO在1GHz的ARM A9纯CPU计算需要70秒以上。虽然本实验的模型是“Tinier YOLO”,这个成绩已经获得了相较纯软件计算数十倍的加速。

成绩算不上实时,但足以满足许多创客的项目需求。

4 总结

本文首先进行常规的开箱和初见印象描述;随后尝试解释了ZYNQ这一硬件的特色;最后以目标检测为例,体验了PYNQ的开发流程。

本文只是PYNQ的一篇开箱文。关于Overlay和一些更加深入的特色,如果将来我的项目使用到了,也更深入地再写一下吧。

总之,PYNQ试图将设计流程变得更加友好,Python也迎合了很多软件开发者的口味,overlay提供了某些功能的硬件加速。

我确实看到了PYNQ的诚意,PYNQ确实能将ZYNQ的开发变得友好:至少对于软件开发者,上手不必折腾那一套Vivado+SDK的工具链,而是尽快投入开发。

对于创客,它绝对是一款值得购买的开发板。如果你的某些项目应用,涉及到了视觉和并行计算等等需求,不妨考虑弄一块PYNQ体验一下。

您好,我提个建议,3.3.3第19行建议加一句检测是否为文件夹,jupyter notebook自动产生了隐藏的.ipynb_checkpoints文件夹,运行中不会有任何错误,但是一直卡死,找了一天的问题终于找到了.......

@tecog 14行,说错了

@tecog 谢谢反馈,现在手上没有这块板子了没法修正验证,直接将您的评论置顶了

pip安装时报错信息“ERROR: Command errored out with exit status 128: git clone -q https://github.com/Xilinx/QNN-MO-PYNQ.git /tmp/pip-req-build-3x3ccbz2 Check the logs for full command output.”网上的方法都是将https:换成git,尝试之后还是不行,来请教博主

@luckf 看你的错误有可能是你的本地时间不正确,导致 https 解析失败;或者是你环境的 github dns 解析被污染。

<ul><li>调整时间可以参考 https://cloud.tencent.com/developer/article/1444268</li><li>或者你可以尝试下载这个工程的包然后本地安装</li></ul>你可以再贴一下全部的日志看看

@SPtuan 谢谢博主的回复,的确是pynq-z2开发板的时间有问题,后来自己发现pynq板没有联网,连上网以后便可以正常工作了,系统时间也正确了。

@luckf 你好,我也是这个问题,怎么确认板子有没有正常联网呢?板子用网线和电脑连了,可以正常使用pynq的jupyter了,但还是报错<span>ERROR: Command errored out with exit status 128</span>

你好博主,想请问如果用这块板子 我想外接触摸屏 然后通过python里的pyqt设计自己的界面,移植到开发板上在触摸屏上实现触控功能调用类似摄像头等外接接口来做图像处理吗?主要是想摆脱上位机 只用开发板和触摸屏实现调用和控制以及计算功能 图像处理的参数结果也希望在移植到开发板上的界面上显示 不用电脑

@double HDMI source port (output)

不知道它这个io是接到arm上还是fpga上的,如果在fpga害得搞个gpu软核啥的

然后试试淘宝的树莓派外接屏,可能还要移植驱动

这东西生态很弱,得搜搜看看有没有现成的方案或者文章

[…] 2018-09-23 PYNQ上手体验:以目标检测应用为例 […]

你好博主,小弟有以下几点疑问:

0.请问目前基于PYNQ的深度学习是否有新的突破?是否有类似于基于Pytorch的Yolov3的模型可以用于PYNQ?

1.本博客的项目如何去训练自己的数据集?

您好,例程顺利跑起来了,想问一下如果想换成自己的模型,该怎么修改呢?不是很明白他这些文件是怎么拆分的?

@lee Hi.

这个问题确实很蛋疼,非常惭愧我在这块板子上浅尝辄止了,包括SDSoC和一些框架的移植尝试工作,感到了阻力。

如果不局限在PYNQ,而是整个ZYNQ异构SoC的话,可以看看Xilinx近期发布的软件栈,介绍里提到了一些私有模型的部署

@lee 兄弟你好,请问这个模型如何去训练自己的数据集,按自己的需求实现目标检测呢?

(可以的话可否加个联系方式 我的QQ 316186434)

您好,我安装了QNN-PYNQ 但是from darknet import * 报错是什么原因呢?

报错如下:

ModuleNotFoundError: No module named 'darknet'

@lll Hello,这篇文章更新很久之前,现在的QNN-PYNQ项目可能发生了变化,请留意最新的项目页面的指引

@lll 你好 现在问题解决了吗?我也遇到相同的问题

求问大神PYNQ怎么联网啊

@cctvjack 就我所理解,只要pynq板接入的电脑或局网可以联网,那么pynq板就能正常联网。

用xnor计算就快了,作者BNN里的cnv结构应该就是xilinx的FINN那篇论文,可这两个我都没发现训练后权重转换脚本。大概算了下,如果单纯把输入图像从6464扩到416416,按同样倍率算时间的话,速度应该还会很快。darknet上已经有一个俄罗斯大神开源了xnor的yolo代码,测试了map,xnor的cnv多分类效果很一般,应该是检测的回归比较难拟合,但是类别少的情况下效果很好。拿xnor做语义分割的meanIOU就比较差了,xnor在cnv的分类效果也比较不错。请问你有权重转换脚本吗,我业余时间学fpga,研究的不深,如果有个权重转换程序pynq在开源社区的推广就完美了。

@jimtswu 我记得当时用作者cnv结构的xnor跑cifar10,64×64能到1080FPS左右。之前在github上找到另一个用

pynq开源的int16的yolo,他前端比较重,我测试是2.7s一帧,大概和作者这个差不多。

@jimtswu 我倒是对权重转换和XNOR没有研究。 大概是半年前吧,老板突然对FPGA感兴趣,让人去弄,然而作为一个软件开发的去深入底层非常吃力,只能从开源社区的资源逐步上手。用的最多的框架是Darknet,甚至把它移植到了SDx上。最关键的是,感觉自己半年来也没有接触到精髓,反而将时间浪费在底层的各种不重要的东西上了。 倒是一直用TX2非常顺手——完整的CUDA生态+系统环境。这东西在快速发展,没有强大的生态撑腰的硬件注定不好用。 前几天去了北京的Xilinx开发者大会,深鉴科技最近又要大动作,我只能说,他的生态会有什么变化,让我们拭目以待吧。

请教一下,我在PYNQ-z2上安装QNN-MO-PYNQ,使用的这里的命令行,结果不行,如果是PYNQ-Z2的话,用什么命令行?

@王竞泽 请贴一下错误提示

@王竞泽 你好,你的问题可能是pip版本问题。PYNQ预构建镜像包含数个Python3版本。印象里,其中 python3/pip3 是指Python3.4,该环境下甚至没有pynq的base库。

解决方案: 尝试使用 pip3.6

sudo pip3.6 install git+https://github.com/Xilinx/QNN-MO-PYNQ.git

欢迎反馈

@SPtuan 使用pip3.6命令行无法运行,直接就会报错

@大头虾 用pip3就行,sudo pip3 install git+https://github.com/Xilinx/QNN-MO-PYNQ.git

@SPtuan 你好,我在使用命令行安装git上的QNN-MO-PYNQ时也遇到了安装不上的问题,用的命令是sudo pip3.6 install git+https://github.com/Xilinx/QNN-MO-PYNQ.git,报错信息如下所示,请问问题出在哪了呢?

报错信息:(可能有点长...)

Collecting git+https://github.com/Xilinx/QNN-MO-PYNQ.git

Cloning https://github.com/Xilinx/QNN-MO-PYNQ.git to /tmp/pip-req-build-98zbzfu0

Installing collected packages: qnn-loopback

Running setup.py install for qnn-loopback ... error

Complete output from command /opt/python3.6/bin/python3.6 -u -c "import setuptools,tokenize;file='/tmp/pip-req-build-98zbzfu0/setup.py';f=getattr(tokenize, 'open', open)(file);code=f.read().replace('\r\n', '\n');f.close();exec(compile(code, file,'exec'))" install --record /tmp/pip-record-ai7125jr/install-record.txt --single-version-externally-managed --compile:

Running pre installation script...

Building hardware library...

Cloning into '/tmp/pip-req-build-98zbzfu0/qnn/src/library/rapidjson'...

Note: checking out 'tags/v1.1.0'.

Command "/opt/python3.6/bin/python3.6 -u -c "import setuptools, tokenize;file='/tmp/pip-req-build-98zbzfu0/setup.py';f=getattr(tokenize, 'open', open)(file);code=f.read().replace('\r\n', '\n');f.close();exec(compile(code, file, 'exec'))" install --record /tmp/pip-record-ai7125jr/install-record.txt --single-version-externally-managed --compile" failed with error code 1 in /tmp/pip-req-build-98zbzfu0/

root@pynq:/home/xilinx# ldes

@Icarus 不好意思回复晚了,这个我也不了解,看样子是rapidjson库安装过程出现问题,尝试单独安装rapidjson库试一试?

@SPtuan 你好,我的问题已经解决了,问题出在image版本上,当时的版本是2.2安装失败,更新到2.3之后安装成功,非常感谢您的回复。

@Icarus 你好,请问下载image哪里有更快的链接?

@王竞泽 我遇到了同样的问题,请问您的问题解决了吗

乖乖